POD DQ ODT Vtt Term VSSQ Term CA ODT No term VSS Term optional. Requiring an interface to one or a range of high-performance DDR5 DDR4 DDR33L DDR2 LPDDR5 LPDDR44X LPDDR3 LPDDR2 LPDDR HBM2 HBM2E and HBM3 SDRAMs or memory.

Understanding Ddr Ddr Protocol Truechip Vips

Designers are increasingly turning to source-synchronous.

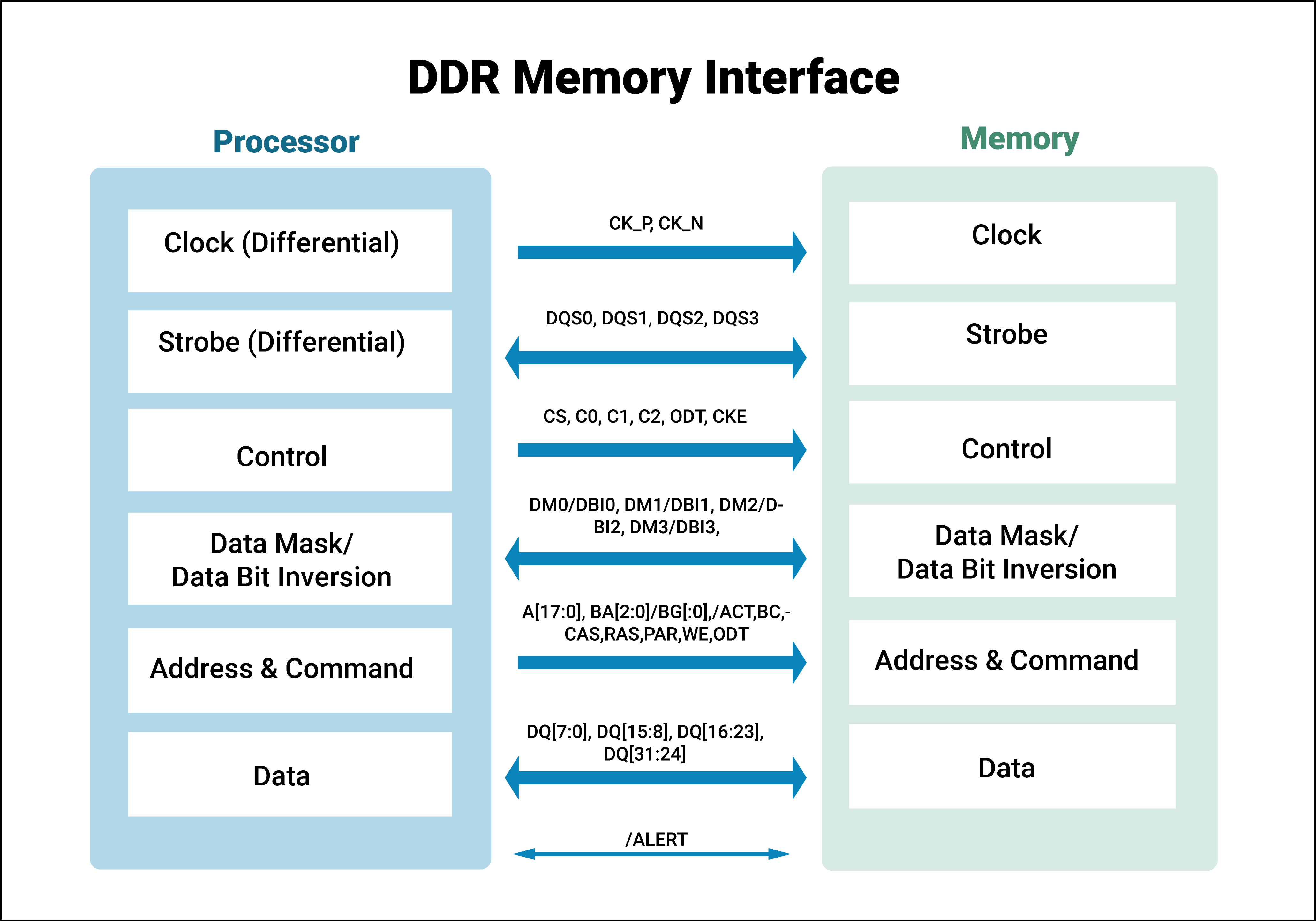

. The DDR SDRAM uses DDR architecture to achieve high-speed operation. The major feature of DDR interface compared to a single data rate SDR one is to use both rising and falling edges of a clock to transfer data which allow it to provide two times the. The designer can choose a fast cycle DRAM like one of Samsungs Network DRAMs.

Building reliable high-speed memory interfaces target FPGA IO structures as well as intellectual property IP used within design software to allow rapid configuration of memory interfaces. As part of the overall design DDR memory controller and memory. By Hansel A Collins and Ronald E Nikel TriCN Associates LLC.

High-Speed DDR4 Memory Designs and Power Integrity Analysis Cuong Nguyen. The design engineer can no longer simply connect data and address lines and expect to have a robust high-speed memory interface. Double Data Rate 3 Synchronous Dynamic Random-Access Memory DDR3 SDRAM is a type of synchronous dynamic random-access memory SDRAM with a high bandwidth double data rate interface and has been in use since 2007It is the higher-speed successor to DDR and DDR2 and predecessor to DDR4 synchronous dynamic random-access memory SDRAM chips.

The Market Need for High Speed Memories SDRAMs have traditionally been used in personal computers PCs. The Denali High-Speed DDR PHY IP provides low latency and up to 4266Mbps throughput while balancing power consumption and minimizing area Developed by experienced teams with industry-leading. Although known for its proprietary and high-performance memory interfaces most notably the RDRAM and more recently the XDR Rambus Corp.

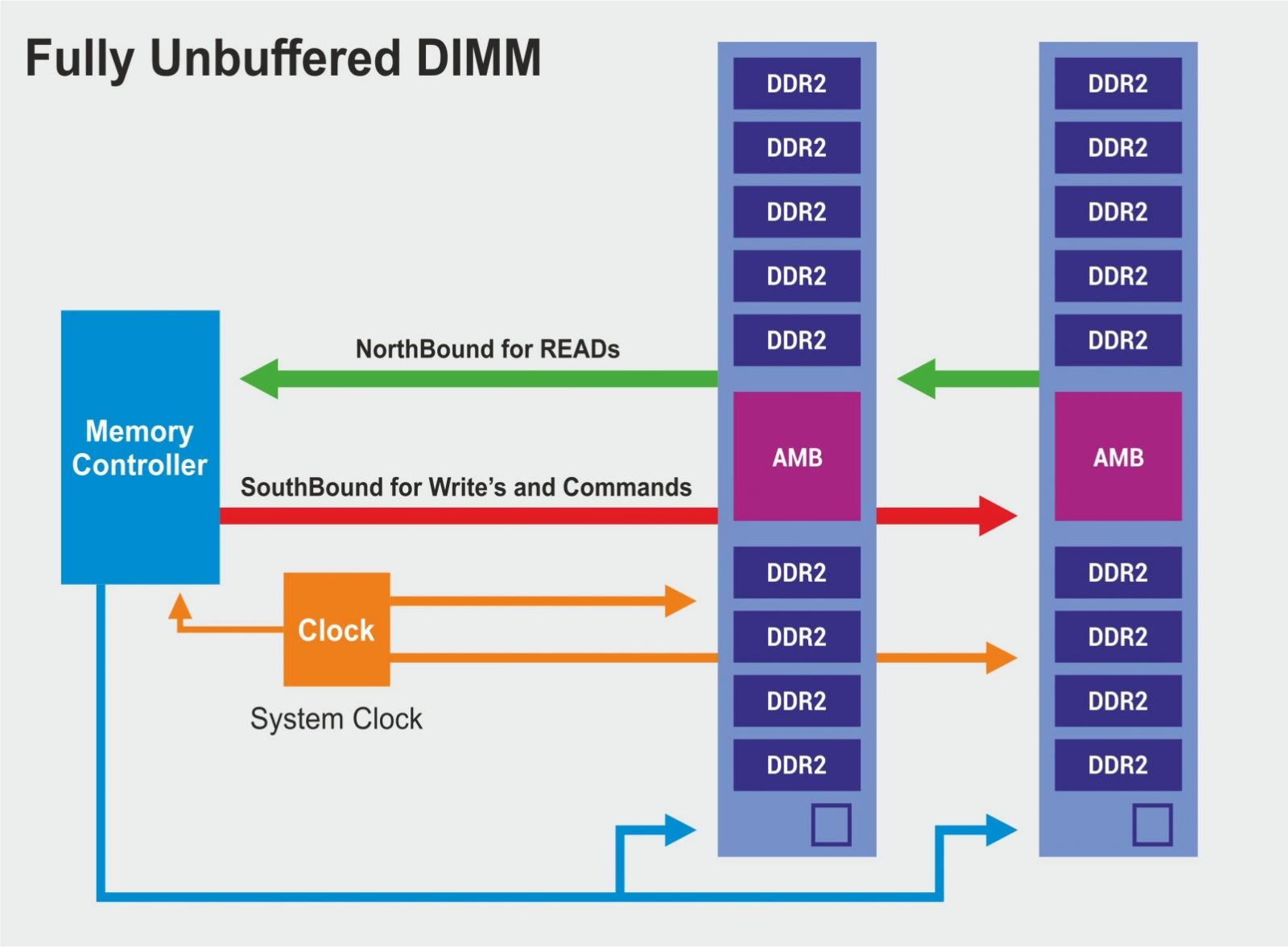

DDR Memory Interface Design Considerations September 30 2011 2011 Micron Technology Inc. These techniques use IP to help gain an extra timing margin at high speed operation. For DDR-I memories JEDEC created and adopted a low voltage high-speed signaling standard called series stub termination logic SSTL.

Or the designer can place a copy of the data in each of the four banks of the DRAM and access the data in a nonactive bank. DDR4 SDRAM operates at high data rate ie from 16Gbps to 32Gbps and the memory interface must be designed in a stringent way to comply with the specification set by JEDEC. DDR-SDRAM high-speed source-synchronous interfaces create design challenges.

High speed DDR memory interface design. External double data rate DDR memory types are a common part of many FPGA designs. As the bandwidth requirement increases Double Data Rate DDR interface is becoming very commonly used in many types.

The major feature of DDR interface compared to a single data rate SDR one is to. Has decided to go mainstream. For High-Speed Memory Controller and PHY Interface AUSTIN Texas May 2 2018 The DDR PHY Interface DFI Group today released version 50 of the specification for interfaces between high-speed memory controllers and physical PHY interfaces to support the requirements of future mobile and server memory standards.

The DesignWare DDR Memory Interface IP provides complete system-level IP solutions for SoCs. DDR SDRAM Main Controller Block Before it is operational the DDR SDRAM memory. As the bandwidth requirement increases Double Data Rate DDR interface is becoming very commonly used in many types of memories such as DDR IIIIII DRAM RLDRAM III QDR IIIII SRAM etc.

The DFI specifications widely. As processor core speeds exceeded 2 GHz revolutionary changes in memory speed efficiency size and costs were required to support these processor enhancements. As the name implies SSTL is.

Of a DDR design is the need to handle and pre-process strobe signals as opposed to generic clock signals. IO Interface HSUL LVSTL 40 IO Power reduction vs. All the major challenges discussed in this paper have to be overcome for excellent signal integrity to guarantee minimum bit error rate in the multi-Gigabit transmission.

Commandsclock topology for high-speed operation in a high-loading condition September 30 2011 2011 Micron Technology Inc. During bringup of the DDR interface the controller turns on differential DQS in the DRAM. Multiple Supported for High Performance IO HPIO Standards Memory IO Standards DDR4 POD12 DDR3 SSTL15 DDR3L SSTL135 LPDDR3 HSUL RLDRAM3 SSTL12 QDR4 HSTLSSTL12V125V POD11V12V QDR2 HSTL12V18V.

Download Citation High speed DDR memory interface design form only given. Doing so will quickly get your design all tangled up. Design verification and debugging - Compliance testing.

SSTL leverage s an active motherboard termination scheme and overcomes the signal integrity concerns with legacy LVTTL signaling. 22 DDR Interface Design Considerations. The Cadence Denali DDR family of high-speed interface IP connects to external memories with the necessary bandwidth for applications.

Traditional interfaces limit interconnect speed to less than 250 MHz and pc-board-interconnect length to approximately 5 in. Working closely with JEDEC Rohde Schwarz provides powerful solutions for DDR compliance testing. DQS needs to be the target of thematched group for each data byte regardless of whether its a single ended or differential signal.

The major feature of DDR interface compared to a single data rate SDR one is to use both rising and falling edges of a clock to transfer data which allow it to provide two times the. Semiconductor IP Core Portal Chip Design Resource. A high-speed interface cell delivers 800 Mbspin data transfer rate on a 26b wide IO interface consisting of a dual-byte data field and a byte-wide command field.

It is not necessary to route the ADDR bus the same length to every chip. High Speed High Performance IO supports many memory interface. Summary form only given.

Hence the IO capacitance is higher than in ASIC design. Bandwidth for device memory. These parts currently have 25-ns tRCs at 200 MHz yielding a 160-Mbps-per-pin bandwidth.

The DDRAM is based on 2n pre-fetch architecture that can achieve two data words per clock pulse at the IO pins for a single read or write access. DDR SDRAMs were introduced as a cost-effective path for upgrading data bandwidth to memory. The company has used its.

As the bandwidth requirement increases Double Data Rate DDR interface is becoming very commonly used in many types of memories such as DDR IIIIII DRAM RLDRAM III QDR IIIII SRAM etc. The need for increasing speed higher memory size and power efficiency is driving the evolution in DDR and LPDDR interface technology as defined by JEDEC. Ad Consult with CDW Experts to Find Compatible Memory for Your Computer Systems.

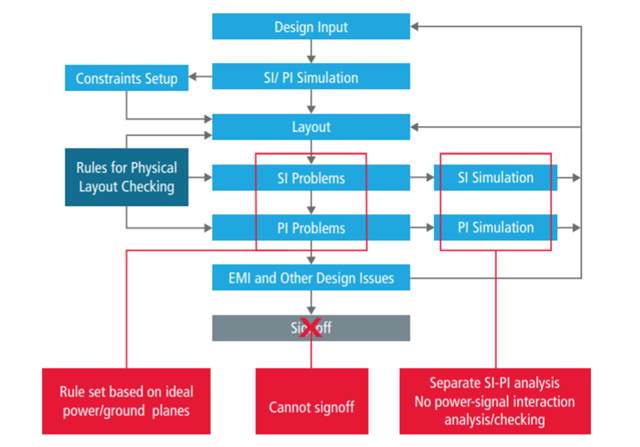

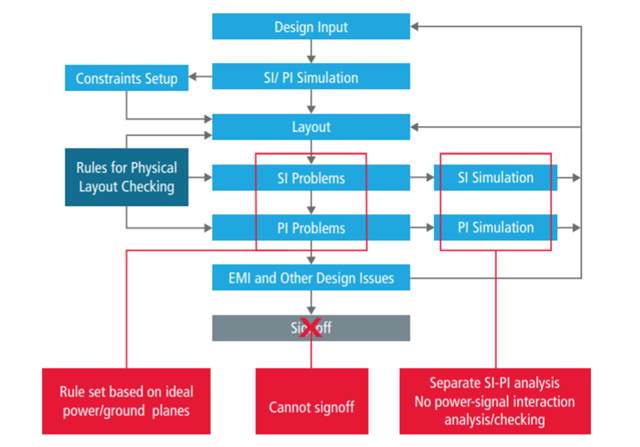

SIPI Analysis in the Design Flow System Design Part Selection and Schematic Entry Prototype PRE-LAYOUT LAYOUT Full Board. As the bandwidth requirement increases Double Data Rate DDR interface is becoming very commonly used in many types of memories such as DDR IIIIII DRAM RLDRAM III QDR IIIII SRAM etc.

How To Successfully Realize A High Speed Memory Interface In Your Design

Implement Si And Pi In High Speed Memory Interfaces Signal And Power Integrity Pcb Ic Packaging Cadence Blogs Cadence Community

How To Successfully Realize A High Speed Memory Interface In Your Design

Ddr Memory Interface Basics 2017 07 05 Signal Integrity Journal

Ddr Memory And The Challenges In Pcb Design Sierra Circuits

Figure 1 From Design And Implementation Of High Speed Ddr Sdram Controller On Fpga Semantic Scholar

.jpg)

0 comments

Post a Comment